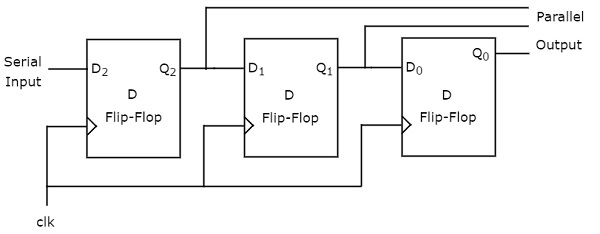

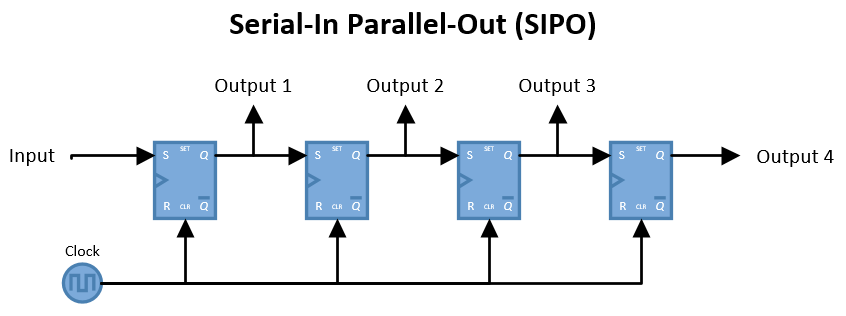

In this project, a 32-bit MIPS ALU was implemented. It contains hhtoh.vhd and sequential_adder.vhd as a component and then connect them properly. top.vhd: This is the top module of the project.This component is used for getting serial inputs from user more easily. hhtoh.vhd: This VHDL code takes the master clock signal as an input signal and then gives a clock signal that has a period of 1 Hz.The final version of the project doesn’t have these files because in the laboratory session, we used a test bench instead of a real time user input. vhd files are present in the Vivado project. For achieving this kind of design, there is also 2 more. The first versions of the project was designed for our FPGA board to make more easy to enter the input numbers in serial manner by the user. This process is also sensitive to an asynchronous reset signal that returns the system to the beginning of the calculation. FSM_SEQ: This process advances the states of algorithm to the next state at each time the clock signal gets high.This section of the sequential adder behaves as the algorithm that described in the bottom of the page 3 of the laboratory paper. FSM_COMB: This is the governor process section of the whole circuit.Also, C output is always the least significant bit of saved summation. When SHIFTC signal is high, the process shifts saved summation value to the right. When the PISOC signal is high, the process saves the summation of the input. This process is governed by the controller. PISO: Outputs the C register in serial manner.REG: When the controller sends a signal, that is LATCHB, the B input loads into the system.SIPO: This process reads the A input in a serial manner at the rising edge of the clock signal for 4 times then converts the input to a paralel manner.All process sections are summarized below. The architecture of sequential_adder.vhd consisting by 5 process sections. It includes a counter used to count the 3 steps of the addition algorithm.

The controller contains the following state machine. Internal structure of the 4-bit sequential adder is shown below: In this project, a primitive two’s complement adder were realized. In the heart of computers along the history, simple computation operators were held very important position. First examples of computers were builded for doing very simple computation works based on common operations such as adding and substracting. The computer is an electronic machine that does computation work. These are my laboratory work from Computer Architecture course. A very simple single cycle and multi cycle MIPS CPU design written in VHDL.

0 kommentar(er)

0 kommentar(er)